## Celebrating 20 Years of the PCle® Specification

PCI-SIG® Webinar Series

April 2024

Copyright © 2024 PCI-SIG. All Rights Reserved

#### **Panelists**

#### Mihaela Erler (Moderator)

Industry Enabling Manager, Intel PCI-SIG® Marketing Work Group Co-Chair

#### **Debendra Das Sharma**

Senior Fellow and Co-GM of Memory and I/O Technologies in Data Platforms and Artificial Intelligence Group, Intel PCI-SIG Board of Directors member

#### **David Harriman**

Distinguished Architect, Ampere Computing PCI-SIG Protocol Work Group Chair and Automotive Work Group Co-Chair

#### **Manisha Nilange**

I/O Architect and Analog Engineering Manager, Intel PCI-SIG ElectroMechanical, Mini and SFF Connector Work Group Chair, Compliance Co-Chair

#### **Richard Solomon**

Technical Marketing Manager, PCIe® Controller IP, Synopsys PCI-SIG Vice President and Compliance Co-Chair

## PCI-SIG®: An Open Industry Consortium

- PCI-SIG: Organization that defines the PCI Express<sup>®</sup> (PCIe<sup>®</sup>) specifications and related form factors

- Established in 1992 32 years and growing stronger – THANK YOU!!

- 975+ member companies worldwide

- Creating specifications and mechanisms to support compliance and interoperability

## PCI SIG

### Evolution of PCI Express® Specification: Speeds and Feeds

- Doubles data rate with full backward compatibility every three years over seven generations

- A x16 PCle<sup>®</sup> 5.0 device interoperates with a x1 PCle 1.0 device!

- Encoding changes when essential

- Ubiquitous I/O across the compute continuum

- PC, Hand-held, Workstation, Server, Cloud, Enterprise, HPC, Embedded, IoT, Automotive and Al

- One stack / same silicon across all segments; supporting

- Different form-factors, widths (x1/ x2/ x4/ x8/ x16) and data rates

| PCle <sup>®</sup><br>Specification | Data Rate(Gb/s)<br>(Encoding) | x16 B/W<br>per direction** | Year  |

|------------------------------------|-------------------------------|----------------------------|-------|

| 1.0                                | 2.5 (8b/10b)                  | 32 Gb/s                    | 2003  |

| 2.0                                | 5.0 (8b/10b)                  | 64 Gb/s                    | 2007  |

| 3.0                                | 8.0 (128b/130b)               | 126 Gb/s                   | 2010  |

| 4.0                                | 16.0 (128b/130b)              | 252 Gb/s                   | 2017  |

| 5.0                                | 32.0 (128b/130b)              | 504 Gb/s                   | 2019  |

| 6.0                                | 64.0 (PAM4, Flit)             | 1024 Gb/s                  | 2022  |

| 7.0                                | 128.0 (PAM4, Flit)            | 2048 Gb/s                  | 2025* |

<sup>\* -</sup> Projected \*\* - bandwidth after encoding overhead

The PCIe specification – Seven generations spanning two decades!

## Q&A

Copyright © 2024 PCI-SIG. All Rights Reserved

## Thank you for attending a PCI-SIG® 2024 Webinar

# For more information, please visit www.pcisig.com

## **Backup Slides**

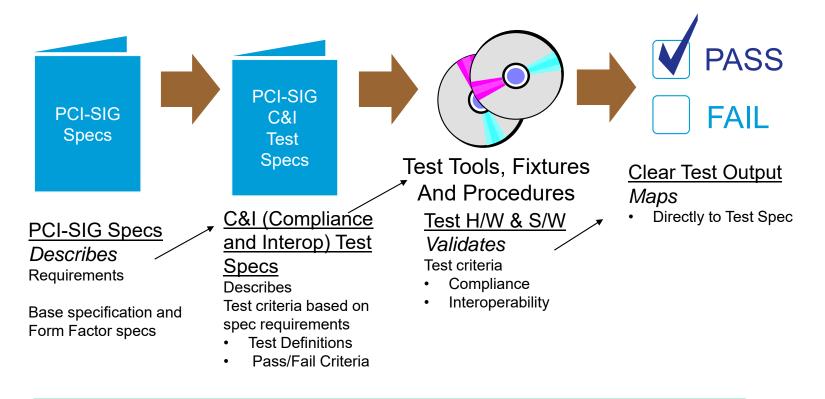

## PCI-SIG®: From Spec to Compliance

Predictable path to design compliance

### PCle® Architecture: One Base Specification, Multiple Form Factors

**BGA**

16x20 mm small and thin platforms

**M.2**

42, 80, and 110mm Smallest footprint of PCIe connector form factors, use for boot or for max storage density U.2 2.5in (aka SFF-8639)

Majority of SSDs sold Ease of deployment, hotplug, serviceability Single-Port x4 or Dual-Port x2 **CEM Add-in-Card**

Add-in-card (AIC) has maximum system compatibility with existing servers and most reliable compliance program. Higher power envelope, and options for height and length

High B/W with PCIe 3.0 Prevalent in hand-held, IoT, automotive

(SFF-TA-1006 – SSD)

(Up to 36 Modules)

(SFF-TA-1007 - SSD)

(Up to 32 Modules)

Source: Intel Corporation

Multiple form-factors from the same silicon to meet the needs of different segments

## **Protocol Evolution to Meet New Usage Models**

- I/O Virtualization

- Data Movement Efficiency across the system

- Transaction Processing Hints, Atomics, Translated vs Untranslated address

- Scalability as system sizes increases:

- Unordered I/O: support fabrics with multipath while maintaining producer-consumer model

- Increased number of outstanding transactions, etc.

- Reliability, Availability, and Serviceability

- Hierarchical Timeout, Advanced Error Reporting, (enhanced) Downstream Port Containment, etc.

- Power Management Enhancements

- Dynamic Power Allocation, L1 Sub-state, L0p, etc.

- Security Enhancements

- Authentication, Encryption, etc.

- And many more ...

Protocol enhancements to meet the (r)evolution in compute landscape over the last two decades