### PCI-SIG<sup>®</sup> Educational Webinar Series 2019

## Retimers to the Rescue: PCI Express<sup>®</sup> Specifications Reach Their Full Potential

### **Presented by Kurt Lender and Casey Morrison**

## Meet the Presenters

Kurt Lender PCI-SIG MWG Chair and IHV Enabling Manager, Data Center Group, Intel Corporation Casey Morrison Head of Systems and Applications, Astera Labs

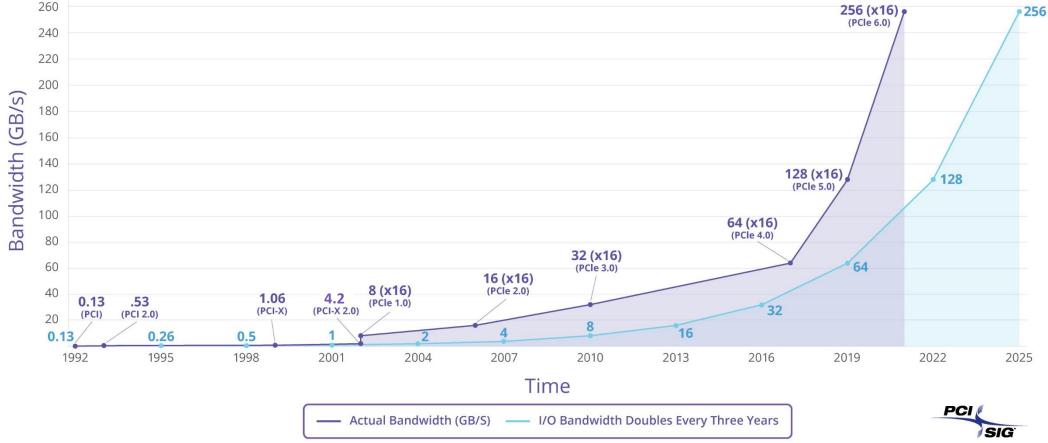

### Introduction – Problem Statement PCIe® Ecosystem Perspective

####

## Introduction – Problem Statement **PCle<sup>®</sup> Ecosystem Perspective**

260

240

220

200

180

160

120

100

80

60

40

0.13

(PCI) 20 0.13

1992

.53

(PCI 2.0)

0.26

1995

8 (x16)

(PCle 1.0)

2004

— Actual Bandwidth (GB/S) — I/O Bandwidth Doubles Every Three Years

4.2 (PCI-X 2.0)

2001

1.06

(PCI-X)

0.5

1998

Bandwidth (GB/s)

PCI

PCI 🦉

SIG

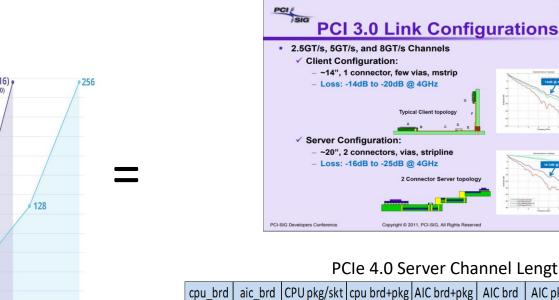

#### **Increasing Gen to Gen Channel Reach Pressures**

#### PCIe 4.0 Server Channel Lengths

| cpu_brd   | aic_brd   | CPU pkg/skt | cpu brd+pkg | AIC brd+pkg | AIC brd | AIC pkg | CPU brd | AIC brd | Total   |

|-----------|-----------|-------------|-------------|-------------|---------|---------|---------|---------|---------|

| material  | material  | [dB]        | [dB]        | [dB]        | [dB]    | [dB]    | ["]     | ["]     | PCB ["] |

|           | low loss  | 4.1         | 18.5        | 6.5         | 3.4     |         | 13.7    | 4       | 17.7    |

| low loss  | mid loss  |             | 16.5        | 8.5         | 5.4     |         | 11.4    | 4       | 15.4    |

|           | high loss |             | 15.1        | 9.9         | 6.8     |         | 9.7     | 4       | 13.7    |

| mid loss  | mid loss  | 4.1         | 16.5        | 8.5         | 5.4     | 3.11    | 7.3     | 4       | 11.3    |

| 1110 1055 | high loss |             | 15.1        | 9.9         | 6.8     |         | 6.3     | 4       | 10.3    |

| high loss | high loss |             | 15.1        | 9.9         | 6.8     |         | 5.1     | 4       | 9.1     |

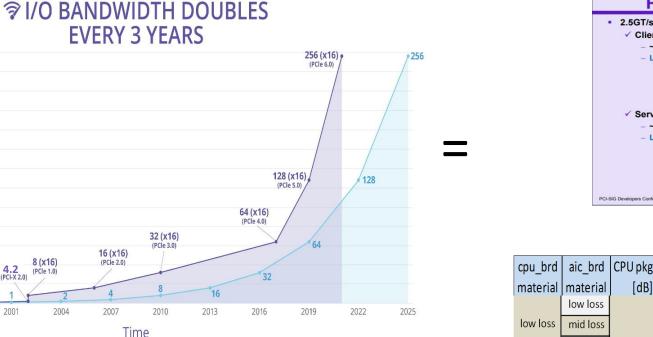

## Introduction – Problem Statement Signal Integrity Perspective

#### Doubling Speed, Reduced Signal Reach

| PCle Rev         | Total<br>channel<br>loss<br>budget | Root<br>Package | Non-root<br>Package | CEM<br>connector    | Add-in<br>Card (AIC) | Budget for<br>system<br>board |

|------------------|------------------------------------|-----------------|---------------------|---------------------|----------------------|-------------------------------|

| 3.0<br>(8 GT/s)  | 22 dB                              | 3.5 dB          | 2.0 dB              | 1.7 dB              | 6.5 dB               | 10.3 dB                       |

| 4.0<br>(16 GT/s) | 28 dB                              | 5.0 dB          | 3.0 dB              | 1.5 dB              | 8.0 dB               | 13.5 dB                       |

| 5.0<br>(32 GT/s) | 36 dB                              | 9.0 dB*         | 4.0 dB*             | 1.5 dB <sup>†</sup> | 9.5 dB†              | 16.0 dB                       |

\*ILfit<sub>TX-ROOT-DEVICE</sub> and ILfit<sub>TX-NON-ROOT-DEVICE</sub> parameters in the base specification. \*Based on CEM 5.0 version 0.5.

**System board budget includes**: vias, stubs, AC coupling capacitor, and microstrip/stripline trace

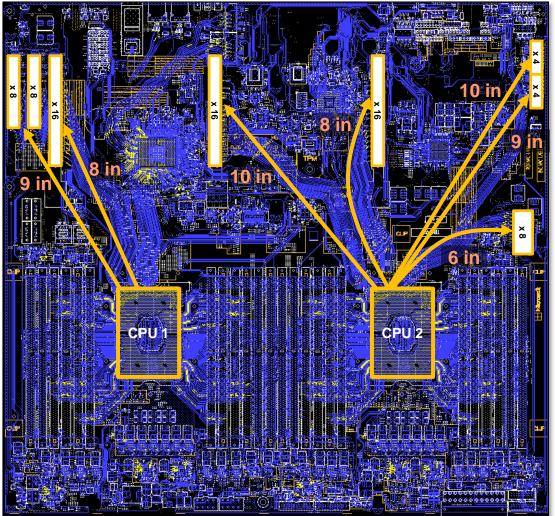

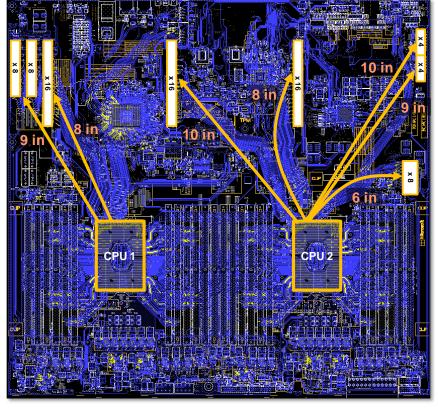

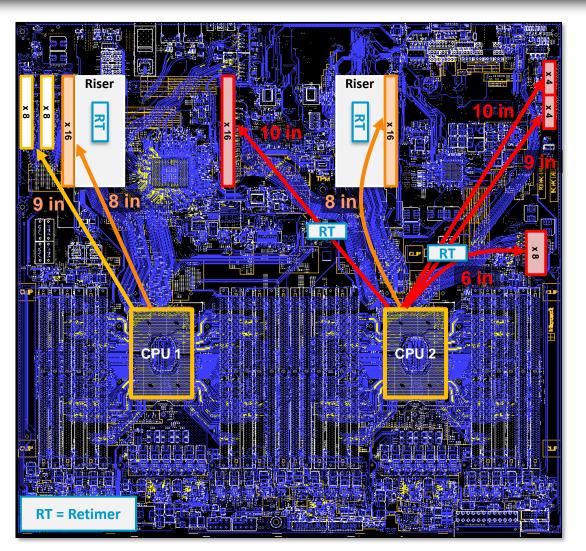

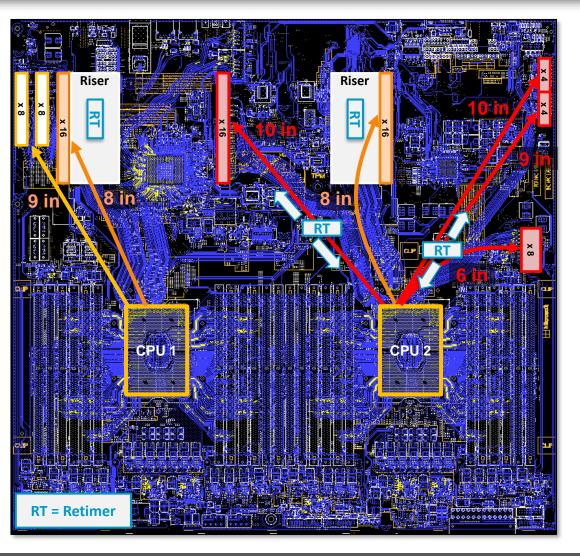

Example: Two-Socket System Board (from OCP)

SIG

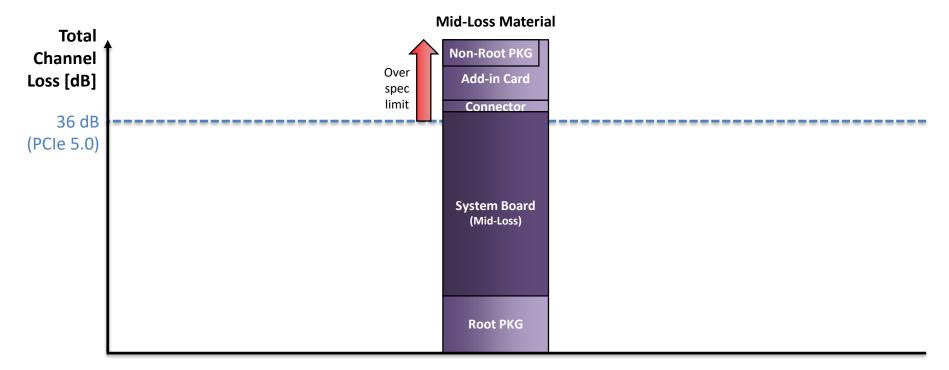

#### **Problem Scenario**

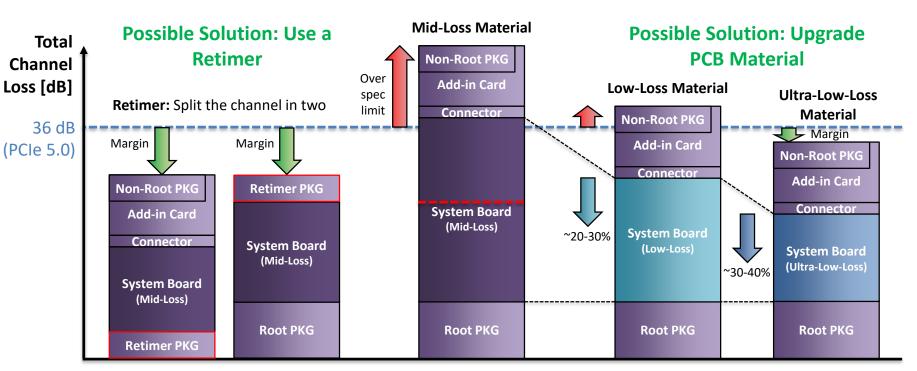

#### **Problem Scenario** Mid-Loss Material **Possible Solution: Upgrade** Total **PCB Material Non-Root PKG** Channel Over Add-in Card Loss [dB] Low-Loss Material spec **Ultra-Low-Loss** limit Connector Material Non-Root PKG 36 dB J Margin Add-in Card (PCle 5.0) Non-Root PKG Connector Add-in Card

System Board (Mid-Loss)

System Board (Low-Loss)

Add-in Card Connector

Root PKG

Root PKG

Root PKG

May not be enough for:

SIG

- Base board >8 in.

- Multi-connector

- Cabled topologies

## Ways to Solve the Signal Integrity Problem

## Ways to Solve the Signal Integrity Problem-

#### **Problem Scenario**

- May not be enough for:

- Base board >8 in.

- Multi-connector

- Cabled topologies

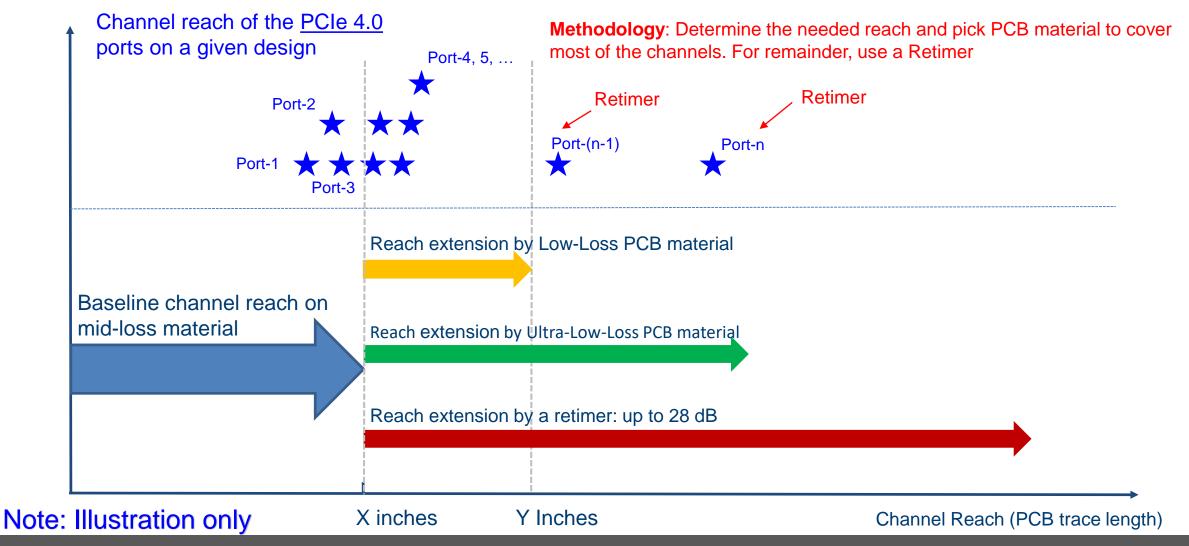

#### **Key Points**

PCI

SIG

- Upgrading PCB material only improves one aspect of total channel: System board

- Even advanced PCB materials may not be enough for longest ports

- Retimers segment the channel into two, creating more margin on each Link segment

## **PCB** Materials

- There is no industry standard definition of **Mid-loss**, **Low-loss**, and **Ultra-low-loss**.

- Actual insertion loss will vary depending on specific material properties, routing layer, trace width, copper roughness, stackup, environment, etc.

- System designers should determine loss numbers which are representative of their design and use case

- The following values are representative examples:

| PCB Material |                                   |                     |          | e unit leng<br>inal Condi<br>(dB/inch) |           | PCB trace unit length loss –<br>Worst-case Conditions<br>(dB/inch) |          |           |

|--------------|-----------------------------------|---------------------|----------|----------------------------------------|-----------|--------------------------------------------------------------------|----------|-----------|

| Category     | Nominal-to-worst-<br>case scaling | Signal routing type | 4<br>GHz | 8<br>GHz                               | 16<br>GHz | 4<br>GHz                                                           | 8<br>GHz | 16<br>GHz |

| Mid-loss     | 16%                               | Stripline           | 0.65     | 1.16                                   | 2.3       | 0.75                                                               | 1.35     | 2.7       |

| 10110-1055   |                                   | Microstrip          | 0.69     | 1.27                                   | 2.4       | 0.80                                                               | 1.47     | 2.8       |

| Low-loss     | 12%                               | Stripline           | 0.50     | 0.85                                   | 1.6       | 0.56                                                               | 0.95     | 1.8       |

| LOW-IUSS     |                                   | Microstrip          | 0.58     | 1.05                                   | 1.8       | 0.65                                                               | 1.18     | 2.0       |

| Ultra        | 8%                                | Stripline           | 0.35     | 0.58                                   | 1.02      | 0.38                                                               | 0.63     | 1.1       |

| low-loss     |                                   | Microstrip          | 0.41     | 0.72                                   | 1.15      | 0.44                                                               | 0.77     | 1.2       |

#### **Key Points**

- Not all "Low-Loss" materials are the same

- It's critical to understand the loss characteristics at worst-case temperature & humidity

## **Reach Implications**

- PCI SIG<sup>®</sup>

- A Link which operates "on the edge"—for example, 1E-12 bit error rate (BER)—will enter Recovery at a rate of once every <u>10 seconds</u>, and it will Replay a TLP every <u>1 second</u> for a x16 Link at 32 GT/s.<sup>[1]</sup>

- The same analysis shows that if the channel loss is reduced by a few dB, BER can improve significantly.

- System designers want peace of mind, and many employ Safety Margin on top of PCIe<sup>®</sup> channel guidelines.

- Safety Margin: self-imposed reduction in channel loss limit to allow for manufacturing variances, simulation-tomeasurement correlation mismatches and other unforeseen degradations affecting system performance.

| Max Reach for Traditiona                              | Key Points |          |                    |          |          |                    |                                          |

|-------------------------------------------------------|------------|----------|--------------------|----------|----------|--------------------|------------------------------------------|

|                                                       | 16 GT/s    |          |                    | 32 GT/s  |          |                    | • At PCIe 5.0                            |

| Case                                                  | Mid-Loss   | Low-Loss | Ultra-<br>Low-Loss | Mid-Loss | Low-Loss | Ultra-<br>Low-Loss | technology speed,<br>"Low-Loss" material |

| Max system board trace,<br>Nominal conditions         | 10.0 in    | 12.7 in  | 18.6 in            | 6.2 in   | 8.6 in   | 13.5 in            | enables ~5-inch<br>system board trace    |

| Max system board trace,<br>Worst-case (WC) conditions | 8.6 in     | 11.4 in  | 17.3 in            | 5.3 in   | 7.7 in   | 12.5 in            | <ul> <li>Upgrading to "Ultra-</li> </ul> |

| Max system board trace,<br>WC and 15% safety margin   | 5.6 in     | 7.5 in   | 11.3 in            | 3.4 in   | 4.8 in   | 7.9 in             | low-loss" will enable<br>~8 inches.      |

[1] PCI-SIG® DevCon 2019, "Impact of Bit Errors in PCIe 5.0 for Latency-Critical Applications," https://members.pcisig.com/wg/PCI-SIG/document/13087?downloadRevision=active

## **Redrivers and Retimers**

#### o **<u>Redriver</u>**

- Analog signals coming in are filtered and/or amplified

- Jitter and noise may get worse or at least stay the same

#### o <u>Retimer</u>

- Analog signals become data inside device, and data is retransmitted

- Can fully regenerate signals, but at a latency cost

• "Repeater" is a superset term used to refer to both (caution: use of this term may cause confusion)

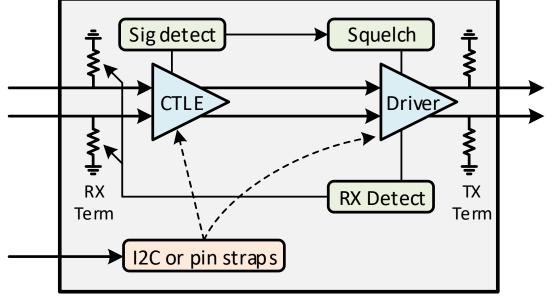

## What is a Redriver?

**Redriver:** Non-protocol-aware softwaretransparent extension device<sup>[1]</sup>

- Mostly analog, designed to boost highfrequency portions of a signal

- Data path typically includes a continuous time linear equalizer (CTLE), a wideband gain stage, and linear driver

- Redrivers do not compensate uncorrelated jitter (e.g. RJ, uncorrelated deterministic jitter, etc.)

- Redrivers do not participate in Link EQ

- No formal standard or compliance program

**Redriver block diagram**

Read more in this PCI-SIG blog paper: <u>https://pcisig.com/pci-express%C2%AE-retimers-vs-</u> <u>redrivers-eye-popping-difference</u>

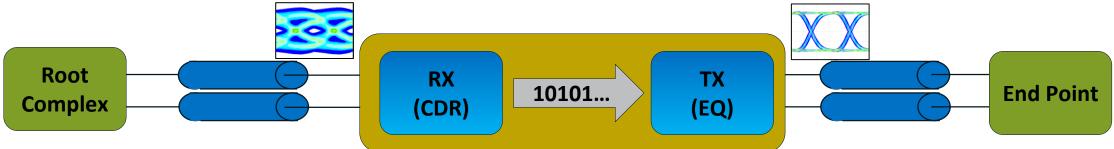

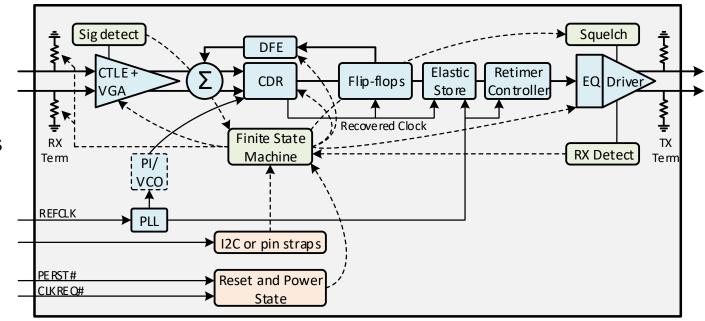

## What is a Retimer?

**Retimer**: A physical layer protocol-aware, software-transparent extension device<sup>[1]</sup>

- Covered in PCIe<sup>®</sup> 4.0 & PCIe 5.0 specifications (Section 4.3)

- Mixed-signal analog/digital device—fully recovers data, extracts clock, and retransmits clean data

- Complies with all PCIe electrical specifications

- Performs Receiver detection and Lane-to-Lane deskew

- Executes Link equalization Phases 2 & 3

- Supports "Equalization to highest rate" and "No equalization needed" PCIe modes

**Retimer block diagram**

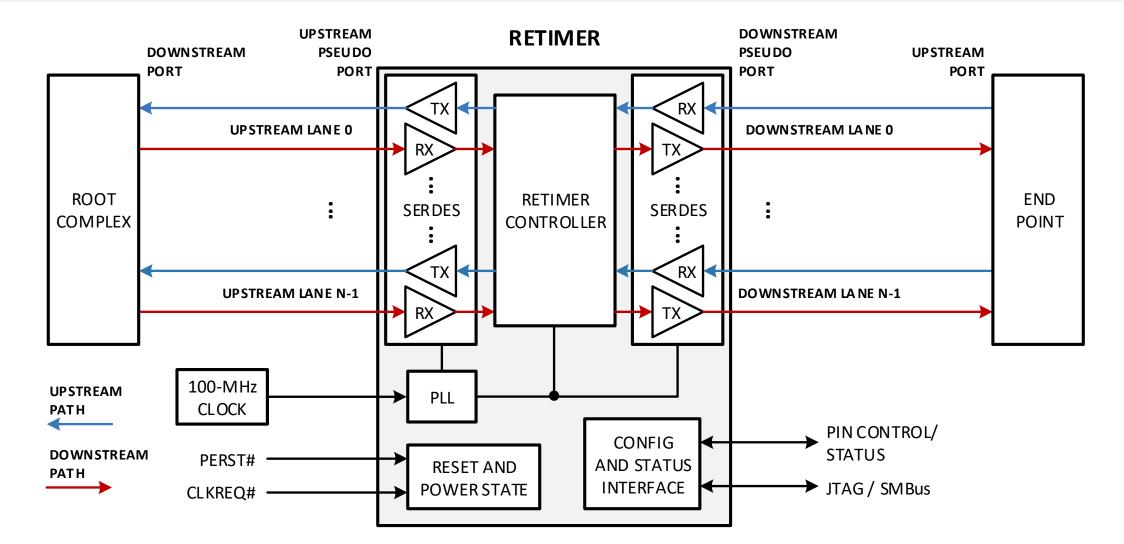

## Retimers in a System

## Reach Extension Solutions Comparison

|          | PCB Material                                                                                                                             | Retimer                                                                                                                                                                            | Redriver                                                                                                                                                                 |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pros     | <ul> <li>Enables modest reach<br/>extension for PCIe 4.0 and<br/>PCIe 5.0 specifications</li> <li>No power or latency impact</li> </ul>  | <ul> <li>Enables 2x to 3x PCIe<sup>®</sup> channel<br/>loss with conventional PCB<br/>material</li> <li>Supported by PCIe 4.0 and 5.0<br/>specs with compliance program</li> </ul> | <ul> <li>Enables modest reach extension<br/>up to PCIe 4.0 technology but<br/>vendor specific</li> <li>Minimal impact to latency</li> </ul>                              |

| Cons     | <ul> <li>Impacts the cost of the whole<br/>PCB</li> <li>Only enables up to 5-8 inches<br/>at 32 GT/s</li> </ul>                          | <ul> <li>Adds power and latency</li> <li>Impacts BoM cost for select ports</li> </ul>                                                                                              | <ul> <li>Not defined in PCIe Base<br/>Specification</li> <li>No formal compliance test</li> <li>Some impact to power and Bill<br/>of Materials (BoM) cost</li> </ul>     |

| Comments | <ul> <li>Margin must be kept for AIC<br/>and Root Port package</li> <li>May still require off-board<br/>extension for storage</li> </ul> | <ul> <li>Usable in open-slot and closed<br/>systems</li> </ul>                                                                                                                     | <ul> <li>More viable for closed-slot<br/>systems</li> <li>Some applications up to PCIe<br/>4.0 technology given sufficient<br/>amount of testing is performed</li> </ul> |

- PCI Express<sup>®</sup> Retimer Test Specification currently at Rev 0.9

- Currently in "FYI testing" phase

- Intent of the Test Specification is to confirm a stand-alone Retimer is compliant to the PCIe 4.0 Base Specification

- Coverage not all inclusive

- Electrical Tests

- Test Macros (Reset, Forwarding, Speed Change, Electrical Idle, etc.)

- Logical Retimer Tests

- Interoperability tests

- Architecture PHY Tests

## Designing with a Retimer High-Level Methodology

1. Scope out the range of trace lengths needed for the system.

Example:

| Link                                      | Max<br>speed<br>required | Approx.<br>Length | Special topology considerations |

|-------------------------------------------|--------------------------|-------------------|---------------------------------|

| Slot 1: x8 for SSDs or accelerator        | 16.0 GT/s                | 9 in              | Standard AIC                    |

| Slot 2: x8 for SSDs or accelerator        | 16.0 GT/s                | 9 in              | Standard AIC                    |

| Slot 3: x16 for NIC or<br>GPU/Accelerator | 32.0 GT/s                | 8 in              | Standard AIC or<br>Riser        |

| Slot 4: x16 for NIC or GPU/Accelerator    | 32.0 GT/s                | 10 in             | Standard AIC or<br>Riser        |

| Slot 5: x16 for NIC or<br>GPU/Accelerator | 32.0 GT/s                | 8 in              | Standard AIC or<br>Riser        |

| Slot 6: x4 for SSDs                       | 16.0 GT/s                | 10 in             | Internal cable                  |

| Slot 7: x4 for SSDs                       | 16.0 GT/s                | 9 in              | Internal cable                  |

| Slot 8: x8 for SSDs                       | 16.0 GT/s                | 6 in              | Internal cable                  |

2. Chose a combination of PCB material and Retimer to meet system performance and cost requirements

#### Example:

| Link                                   | Max speed Appro |        | Special topology      | I        | Note     |                |   |

|----------------------------------------|-----------------|--------|-----------------------|----------|----------|----------------|---|

|                                        | required        | Length | considerations        | Mid-Loss | Low-Loss | Ultra-Low-Loss |   |

| Slot 1: x8 for SSDs or accelerator     | 16.0 GT/s       | 9 in   | Standard AIC          | Yes      | Maybe    | No             | 1 |

| Slot 2: x8 for SSDs or accelerator     | 16.0 GT/s       | 9 in   | Standard AIC          | Yes      | Maybe    | No             | 1 |

| Slot 3: x16 for NIC or GPU/Accelerator | 32.0 GT/s       | 8 in   | Standard AIC or Riser | Yes      | Yes      | Maybe          | 1 |

| Slot 4: x16 for NIC or GPU/Accelerator | 32.0 GT/s       | 10 in  | Standard AIC or Riser | Yes      | Yes      | Maybe          | 2 |

| Slot 5: x16 for NIC or GPU/Accelerator | 32.0 GT/s       | 8 in   | Standard AIC or Riser | Yes      | Yes      | Maybe          | 1 |

| Slot 6: x4 for SSDs                    | 16.0 GT/s       | 10 in  | Internal cable        | Yes      | Yes      | Maybe          | 3 |

| Slot 7: x4 for SSDs                    | 16.0 GT/s       | 9 in   | Internal cable        | Yes      | Yes      | Maybe          | 3 |

| Slot 8: x8 for SSDs                    | 16.0 GT/s       | 6 in   | Internal cable        | Yes      | Maybe    | Maybe          | 3 |

Notes:

- 1: Need for Retimer depends on whether you want to reserve safety margin or not.

- 2: With ultra-low-loss material, if a riser card is used, then a Retimer will likely be required on the Riser.

- 3: Depends on length of cable and number of connectors, but typically >2 connectors will necessitate a Retimer.

- 3. Identify opportunities to group ports requiring a Retimer together to reduce solution size

- Multiple x4 and/or x8 Links can utilize a single x16 Retimer, using **bifurcation** as needed.

# 4. Determine optimum placement for the Retimer(s)

- Place close enough to the slot to allow for a variety of cards and cables to be used, including *passive* riser cards.

- Consider air flow and routing density.

**Bifurcation**: Segmenting a xN device (e.g. N=16) into multiple, smaller Links (e.g. x4x4x8).

PC

SIG

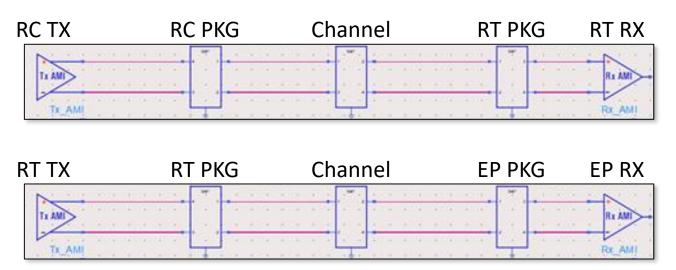

- 5. Check Signal Integrity (SI) by running IBIS-AMI simulations, adjust placement as necessary

- A Retimer has two Link segments: RC-to-RT and RT-to-EP

- Each can be simulated independently through SeaSim (to assess the passive channel) or IBIS-AMI (to assess the channel plus RC, RT, and RP).

## **Retimer Diagnostic Capabilities**

#### **Standard Diagnostic Capabilities**

#### • Slave Loopback

- Optional feature in PCIe<sup>®</sup> Base Spec

- Allows data to loop back from RC to RT or from EP to RT

#### • Receiver Margining

- Like any PCIe receiver, Retimers must support Receiver Margining via Control SKP Ordered Sets

- Eye opening can be assessed on BOTH Pseudo Ports

#### In-Band Register Reads

- Read status information from the Retimer via in-band Control SKP Ordered Sets

- This, unfortunately, requires the Link to be up

#### **Other Possible Diagnostic Capabilities**

#### • Full Eye Capture

Recording the shape of the eye, beyond just the timing and voltage margin reported by Receiver Margining

#### • Protocol Status Reporting

- A Retimer is aware of the physical layer protocol events on both the Upstream and Downstream Pseudo Ports.

- It can record this information and report it to a system controller as needed to facilitate Link debug

- It can possible generate interrupts to a system controller on important events (e.g. unexpected entry to Recovery)

- With Speeds increasing, the need for Retimers will continue to increase.

- PCIe 6.0 specification is planning for 64 GT/s using PAM4 signaling and targeting similar channel reach as PCIe 5.0 specification.

- Retimers will need to support the same 64 GT/s PAM4 signaling and operate within the BER constraints required for a low-latency forward error correction (FEC).

- <u>Low latency</u> is key for many emerging PCIe applications: machine learning, artificial intelligence, distributed computing

- Retimers must innovate along with RCs and EPs to keep PCIe Links fast, low-power, and low-latency.

PCI-SIG members have access to the PCIe<sup>®</sup> specification library. If you would like to learn more about joining, please visit the PCI-SIG website:

https://pcisig.com/membership/become-member

# **Questions?**

# **Thank You For Attending**