#### **Notice Notice Notice Notice Notice Notice Notice Notice**

## PCI-SIG ENGINEERING CHANGE NOTICE

| TITLE:             | Transition of NFC Signals from 3.3V to 1.8V    |  |  |

|--------------------|------------------------------------------------|--|--|

| DATE:              | October 19, 2014                               |  |  |

| AFFECTED DOCUMENT: | M.2 Spec Rev 1.0                               |  |  |

| SPONSOR:           | Manisha Nilange and Ra'anan Sover; Intel Corp. |  |  |

#### Part I

#### 1. Summary of the Functional Changes

The proposed change is to change the current voltage level of the NFC related signals (I2C DATA, I2C CLK and ALERT#) on the Connectivity pinouts and definitions from 3.3V to 1.8V signal level to better align with future platforms operating signal levels typical in the industry.

The change is being proposed to simply change the definition in the spec because no one in the WG has given any indication that the NFC signals are being used at their current 3.3V definition nor are they planning to use them at 3.3V in the near future.

#### 2. Benefits as a Result of the Changes

To better align with theindustry transition to 1.8V IO signal levels both on platform

#### 3. Assessment of the Impact

No known impact

#### 4. Analysis of the Hardware Implications

No expected contention because no one seems to have ever used or wired up these signals.

#### 5. Analysis of the Software Implications

N/A.

#### 6. Analysis of the C&I Test Implications

N/A.

#### **Notice Notice Notice Notice Notice Notice Notice Notice Notice**

## Part II

#### **Detailed Description of the change**

#### Change Table 15 as follows:

Change Table 22 as follows:

Table 22. SDIO Based Module Solution Pinout (Module Key E)

|                 |    |                              | GND                     | 75 |

|-----------------|----|------------------------------|-------------------------|----|

|                 | 74 | 3.3V                         | RESERVED/REFCLKn1       | 73 |

|                 | 72 | 3.3V                         | RESERVED/REFCLKp1       | 71 |

|                 | 70 | UIM_POWER_SRC/GPIO1/PEWAKE1# | GND                     | 69 |

|                 | 68 | UIM_POWER_SNK/CLKREQ1#       |                         |    |

|                 | 66 | UIM SWP/PERST1#              | RESERVED/PETn1          | 67 |

|                 | 64 | RESERVED                     | RESERVED/PETp1          | 65 |

| _               |    |                              | GND                     | 63 |

| $\rightarrow$   | 62 | ALERT#(0)(0/1.8V)            | RESERVED/PERn1          | 61 |

| $\rightarrow$   | 60 | I2C_CLK (I)(0/1.8V)          | RESERVED/PERp1          | 59 |

| <del>&gt;</del> | 58 | I2C_DATA (I/O)(0/1.8V)       | GND                     | 57 |

|                 | 56 | W_DISABLE1#(I)(0/3.3V)       |                         | 55 |

|                 | 54 | W_DISABLE2#(I)(0/3.3V)       | PEWAKE0# (I/O) (0/3.3V) |    |

|                 | 52 | PERST0# (I)(0/3.3V)          | CLKREQ0# (I/O)(0/3.3V)  | 53 |

|                 | 50 | SUSCLK(32kHz) (I)(0/3.3V)    | GND                     | 51 |

|                 |    |                              | REFCLKn0                | 49 |

|                 | 48 | COEX1 (I/O) (0/1.8V)         | REFCLKp0                | 47 |

|                 | 16 | COEV2(I/O\(0/1.9\/\          |                         |    |

## **Notice Notice Notice Notice Notice Notice Notice Notice**

Change Table 23 as follows:

Table 23. Display Port Based Module Solution Pinout (Module Key A)

|                   | 74 | 3.3V                      | GND                    | 75 |

|-------------------|----|---------------------------|------------------------|----|

|                   |    |                           | REFCLKn1               | 73 |

|                   | 72 | 3.3V                      | REFCLKp1               | 71 |

|                   | 70 | PEWAKE1# (I/O)(0/3.3V)    | GND                    | 69 |

|                   | 68 | CLKREQ1# (I/O)(0/3.3V)    | PETn1                  | 67 |

|                   | 66 | PERST1# (I)(0/3.3V)       |                        | 65 |

|                   | 64 | RESERVED                  | PETp1                  |    |

| $\longrightarrow$ | 62 | ALERT# (O)(0/1.8V)        | GND                    | 63 |

|                   | 60 | I2C_CLK (I)(0/1.8V)       | PERn1                  | 61 |

|                   | 58 | I2C DATA (I/O)(0/1.8V)    | PERp1                  | 59 |

|                   | 56 | W DISABLE1#(I)(0/3.3V)    | GND                    | 57 |

|                   | 54 | W DISABLE2# (I)(0/3.3V)   | PEWAKE0# (I/O)(0/3.3V) | 55 |

|                   | 52 | PERSTO# (1)(0/3.3V)       | CLKREQ0# (I/O)(0/3.3V) | 53 |

|                   |    | 1117                      | GND                    | 51 |

|                   | 50 | SUSCLK(32kHz) (I)(0/3.3V) | REFCLKn0               | 49 |

Change Table 24 as follows:

Table 24. Socket 1 Module Pinout with Dual Module Key (A-E)

|               | 74        | 3.3V                         | GND                     | 75  |

|---------------|-----------|------------------------------|-------------------------|-----|

|               | 74        |                              | RESERVED/REFCLKn1       | 73  |

|               | 72        | 3.3V                         | RESERVED/REFCLKp1       | 71  |

|               | 70        | UIM_POWER_SRC/GPIO1/PEWAKE1# | GND                     | 69  |

|               | 68        | UIM_POWER_SNK/CLKREQ1#       |                         |     |

|               | 66        | UIM SWP/PERST1#              | RESERVED/PETn1          | 67  |

|               | 64        | RESERVED                     | RESERVED/PETp1          | 65  |

|               |           |                              | GND                     | 63  |

| -             | 62        | ALERT# (O)(0/1.8V)           | RESERVED/PERn1          | 61  |

| $\rightarrow$ | <b>60</b> | 12C_CLK (1)(0/1.8V)          | RESERVED/PERp1          | 59  |

| $\rightarrow$ | 58        | I2C_DATA (I/O)(0/1.8V)       |                         |     |

|               | 56        | W DISABLE1#(I)(0/3.3V)       | GND                     | 57  |

|               | 54        | W DISABLE2# (I)(0/3.3V)      | PEWAKE0# (I/O)(0/3.3V)  | 55  |

|               |           |                              | CLK REQ0# (I/O)(0/3.3V) | 53  |

|               | 52        | PERST0# (I)(0/3.3V)          | GND                     | 51  |

|               | 50        | SUSCLK(32kHz) (I)(0/3.3V)    | REFCLKn0                | 49  |

|               | 48        | COEX1 (I/O)(0/1.8V)          | HET CENTIO              | 7.5 |

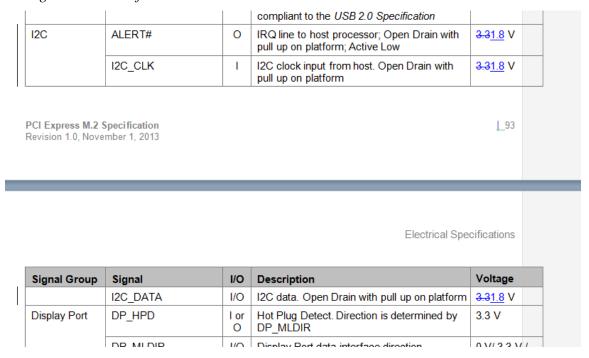

*Update text in Chapter 4.1 as follows:*

# 4.1. 3.3 V Logic Signal Requirements

The 3.3 V card logic levels for single-ended digital signals (WAKE#, CLKREQ#, PERST#, SUSCLK, W\_DISABLE#, UART\_WAKE, 12C, DP\_MLDIR, LED#) are given in Table 36.

Table 36. DC Specification for 3.3 V Logic Signaling

| H  |        |                    |           |       |       |      |       |

|----|--------|--------------------|-----------|-------|-------|------|-------|

|    | Symbol | Parameter          | Condition | Min   | Max   | Unit | Notes |

| -  | +3.3 V | Supply Voltage     |           | 3.135 | 3.465 | V    |       |

| \  | Vін    | Input High Voltage |           | 2.0   | 3.6   | V    |       |

| Ι, | 1      | Input Low Voltago  |           | 0.5   | 0.0   | 17   |       |

*Update text in Chapter 4.2 as follows:*

# 4.2. 1.8 V Logic Signal Requirements

The 1.8 V card logic levels for single-ended digital signals (SDIO, UART, <a href="L2C">L2C</a>. PCM/I2S, etc.) are given in Table 37.

Table 37. DC Specification for 1.8 V Logic Signaling

| Symbol            | Parameter           | Condition               | Min                     | Max                    | Unit | Notes |

|-------------------|---------------------|-------------------------|-------------------------|------------------------|------|-------|

| V <sub>DD18</sub> | Supply Voltage      |                         | 1.7                     | 1.9                    | V    |       |

| ViH               | Input High Voltage  |                         | 0.7*V <sub>DD18</sub>   | V <sub>DD18</sub> +0.3 | V    |       |

| VIL               | Input Low Voltage   |                         | -0.3                    | 0.3*V <sub>DD18</sub>  | V    |       |

| Vон               | Output High Voltage | Iон = -1mA<br>VDD18 Min | V <sub>DD18</sub> -0.45 |                        | V    |       |

| Voi               | Output Low Voltage  | lo∟ − 1m∆               |                         | 0.45                   | V    |       |

Change Table 44 as follows:

Table 44. Socket 1-DP Pin-Out Diagram (Mechanical Key A) On Platform

|               |    | 0.014                     | GND                     | 75 |

|---------------|----|---------------------------|-------------------------|----|

|               | 74 | 3.3V                      | REFCLKn1                | 73 |

|               | 72 | 3.3V                      | REFCLKp1                | 71 |

|               | 70 | PEWAKE1#(I/O)(0/3.3V)     | GND                     | 69 |

|               | 68 | CLKREQ1# (I/O)(0/3.3V)    |                         |    |

| İ             | 66 | PERST1# (O)(0/3.3V)       | PERn1                   | 67 |

| ŀ             | 64 | RESERVED                  | PERp1                   | 65 |

| _             |    |                           | GND                     | 63 |

| $\overline{}$ | 62 | ALERT# (I)(0/1.8V)        | PETn1                   | 61 |

| $\rightarrow$ | 60 | I2C_CLK (O)(0/1.8V)       | PETp1                   | 59 |

| $\rightarrow$ | 58 | I2C_DATA (IO)(0/1.8V)     | ·                       |    |

|               | 56 | W_DISABLE1# (O)(0/3.3V)   | GND                     | 57 |

| }             | 54 | W_DISABLE2# (O) (0/3.3V)  | P EWAKE0# (I/O)(0/3.3V) | 55 |

| -             |    |                           | CLKREQ0# (I/O)(0/3.3V)  | 53 |

| -             | 52 | PERST0# (O)(0/3.3V)       | GND                     | 51 |

|               | 50 | SUSCLK(32kHz) (O)(0/3.3V) | REFCLKn0                | 49 |

|               | 48 | COEX1 (I/O)(0/1.8V)       |                         |    |

|               |    |                           | REFCLKp0                | 47 |

# **Notice Notice Notice Notice Notice Notice Notice Notice**

Change Table 45 as follows:

Table 45. Socket 1-SD Pin-Out Diagram (Mechanical Key E) On Platform

|               |      |                              | GN D                   | 75 |

|---------------|------|------------------------------|------------------------|----|

|               | 74   | 3.3V                         | RESERVED/REFCLKn1      | 73 |

|               | 72   | 3.3V                         | RESERVED/REFCLKp1      | 71 |

|               | 70   | UIM_POWER_SRC/GPIO1/PEWAKE1# | GND                    | 69 |

|               | 68   | UIM_POWER_SNK/CLKREQ1#       |                        |    |

|               | 66   | UIM_SWP/PERST1#              | RESERVED/PERn1         | 67 |

|               | 64   | RESERVED                     | RESERVED/PERp1         | 65 |

| _             | - 62 | ALERT#(I)(0/1.8V)            | GND                    | 63 |

| $\overline{}$ |      |                              | RESERV ED/PETn1        | 61 |

|               | 60   | I2C_CLK (O)(0/1.8V)          | RESERVED/PETp1         | 59 |

|               | > 58 | I2C_DATA (I/O)(0/1.8V)       | GND                    | 57 |

|               | 56   | W_DISABLE1#(O)(0/3.3V)       | PEWAKE0# (I/O)(0/3.3V) | 55 |

|               | 54   | W_DISABLE2# (O)(0/3.3V)      | 11 11 1                |    |

|               | 52   | PERSTO#(O)(0/3.3V)           | CLKREQ0# (I/O)(0/3.3V) | 53 |

|               | 50   | SUSCLK(32kHz) (O)(0/3.3V)    | GND                    | 51 |

|               | 40   | 50514 (10) (2(3, 7.1)        | REFCLKn0               | 49 |