# PCI Express® Architecture: Driving the Future of Storage I/O

### Ramin Neshati, Ph.D.

Member, PCI-SIG Board of Directors

Chair, PCI-SIG Marketing Workgroup

### Recent Storage Industry Trends

□ PCIe<sup>™</sup> Technology as Storage Interconnect

Summary & Call to Action

2015 Storage Developer Conference. © PCI-SIG ®. All Rights Reserved.

SIG

PCI

# **Storage Industry Trends**

Massive growth in data driving SSD adoption

Anticipated growth to \$10B by 2018

Robust growth in Data Center Storage TAM

SSD adoption growing at faster than 40%

Accelerating NVMe<sup>\*</sup> adoption in Data Center

Over half of Data Center SSDs by 2017

2015 Storage Developer Conference. © PCI-SIG ®. All Rights Reserved.

Source: Forward Insights Q1'15

SIG

PCI

3

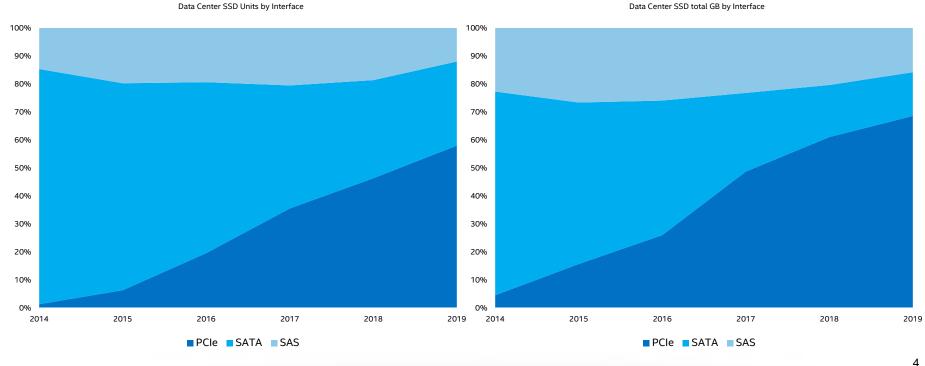

# **Storage Industry Trends**

15

SD

#### PCIe adoption pace makes it <u>the</u> interconnect for storage

Outpacing other interconnects in both units and bandwidth/capacity

4

Source: Forward Insights Q1'15

SIG

PCI

2015 Storage Developer Conference. © PCI-SIG ®. All Rights Reserved.

### Recent Storage Industry Trends

# □ PCIe<sup>™</sup> Technology as Storage Interconnect

### Summary & Call to Action

2015 Storage Developer Conference. © PCI-SIG ®. All Rights Reserved.

SIG

PCI

# **PCIe I/O for Storage – Performance**

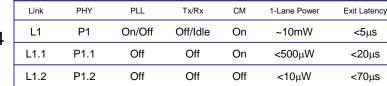

#### PCIe 4.0 specification

- 16GT/s performance w/ high-volume manufacturability

- Backwards compatible to PCIe 1/2/3

- Standardized repeater for long channels (>10", 1 connector)

- Base spec on track for rev0.7 maturity by 4Q'15-1Q'16

- □ Near-0 link idle power

15

L1 Sub-states ECN published in 2014

Status

- □ ½ swing spec for lower link active power

- Available since PCIe 1.1 (circa 2004)

- M-PCIe<sup>™</sup> for PCIe functionality where M-PHY<sup>\*</sup> exists

**Targets**

PCI

6

SIG

Sub-state

# PCIe I/O for Storage – CEM++ Expansion

### □ SFF-8639 (U.2)

Dense packing 2.5" SSDs, hot-plug, serviceable, x1/x2/x4, multi-topology, compliancy

### **M**.2

□ 42/80/110mm, boot or max storage density, client & server compliancy, compliancy

#### OCuLink w/ SRIS

15

Low-cost, low EMI, x1/x2/x4, internal cabling for SATA transition

PCI

SIG

2015 Storage Developer Conference. © PCI-SIG ®. All Rights Reserved.

# **PCIe I/O for Storage – Compliance**

#### Industry-leading compliance program

- MB & AIC test fixtures Test channels for silicon validation

- Sigtest Jitter/voltage noise separation for signal integrity

- CV Configuration space verifier

#### □ SFF-8639 (U.2) & M.2 also supported

- PCI-SIG extending its C&I program to SFF (U.2) & M.2

- □ Initial SFF (U.2) C&I testing completed in August 2015

- Future C&I workshops will integrate M.2 testing

PCI

CBB

SIG

### Recent Storage Industry Trends

### □ PCIe<sup>™</sup> Technology as Storage Interconnect

# Summary & Call to Action

2015 Storage Developer Conference. © PCI-SIG ®. All Rights Reserved.

SIG

PCI

- SSD attach is transitioning to PCIe interconnect

- PCIe architecture is all you need for storage applications in any device or system topology

- PCI-SIG has numerous form factors for increased flexibility in storage I/O expansion

- PCI-SIG has robust compliance program for end-to-end interoperability

- PCIe 4.0 architecture provides unbeatable performance headroom with low power features

#### Visit <u>www.pcisig.com</u> for more info on PCIe technology!

SIG

PCI

2015 Storage Developer Conference. © PCI-SIG ®. All Rights Reserved.